科技工作者之家

科界APP是专注科技人才,知识分享与人才交流的服务平台。

科技工作者之家 2019-11-23

来源:中国国际技术转移中心

目前,用于计算机处理器的硅集成电路正接近单个芯片上晶体管的最大可行密度,至少在二维阵列中是这样。摩尔定律看似已难以维持。美国密歇根大学一研究团队却另辟蹊径,将晶体管阵列带入三维空间,在最先进的硅芯片上直接堆叠第二层晶体管。这一研究为开发打破摩尔定律的硅集成电路铺平了道路。

摩尔定律认为,集成电路上可容纳的晶体管数目,约每隔两年便会增加一倍。目前硅集成电路的晶体管密度已接近极限。而随着硅晶体管尺寸变得越来越小,它们的工作电压也在不断下降,导致最先进的处理芯片可能会与触摸板、显示驱动器等高电压接口组件不兼容,后者需要在更高电压下运行,以避免错误的触摸信号或过低亮度设置之类的影响。这就需要额外的芯片来处理接口设备和处理器之间的信号转换。

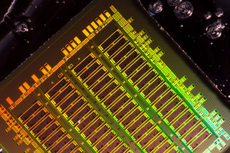

为解决上述问题,密歇根大学研究人员通过附加器件层的单片三维集成,来提高硅互补金属氧化物半导体集成电路的性能。他们首先使用含锌和锡的溶液覆盖硅芯片,在其表面形成均匀涂层,随后短暂烘烤使其干燥,经过不断重复后制成一层约75纳米厚的氧化锌锡膜。使用该氧化锌锡膜制造的薄膜晶体管可以承受比下方硅芯片更高的电压。

为了解决两个器件层之间的电压失配问题,研究人员采用了顶部肖特基、底部欧姆的接触结构,在触点添加的肖特基门控薄膜晶体管和垂直薄膜二极管具有优良的开关性能。测试显示,在集成了高压薄膜晶体管后,基础硅芯片仍然可以工作。

研究人员表示,硅集成电路在低电压(约1伏)下工作,但可以通过单片集成薄膜晶体管来提供高电压处理能力,从而免除了对额外芯片的需求。他们的新方法将氧化物电子学的优势引入到单个硅晶体管中,有助于更紧凑、具有更多功能的芯片的开发。

相关论文刊发在最新一期《自然·电子学》杂志上。

来源:chinaittc 中国国际技术转移中心

原文链接:http://mp.weixin.qq.com/s?__biz=MzA5NjI1MjYwMQ==&mid=2654473839&idx=3&sn=82ece742671a1a23bf0961de2602b765&chksm=8b7e49b9bc09c0afa24dda304faca9ce308305e45a4b637cdd3273419b7a2533dd61973c8bdb&scene=27#wechat_redirect

版权声明:除非特别注明,本站所载内容来源于互联网、微信公众号等公开渠道,不代表本站观点,仅供参考、交流、公益传播之目的。转载的稿件版权归原作者或机构所有,如有侵权,请联系删除。

电话:(010)86409582

邮箱:kejie@scimall.org.cn

30万人才缺口拦路集成电路发展

超薄晶体管让计算机芯片“再快一点”

液态金属有望催生一系列战略性新兴产业

重组计算机芯片:晶体管可同时处理和存储信息

集成电路技术的根本——晶体管的故事

固态热晶体管超高速精确控制热量,开辟计算机芯片热管理新领域

迄今最快AI芯片拥有4万亿个晶体管,将用于构建大型人工智能超级计算机

晶体管逐渐变小,Dennard定律比摩尔定律更值得关注,散热和功耗推动芯片专业化

将光子学与硅纳米电子集成到芯片设计中

量子芯片——从摩尔定律到尼文定律