科技工作者之家

科技工作者之家APP是专注科技人才,知识分享与人才交流的服务平台。

科技工作者之家 2019-12-17

来源:材料科学与工程

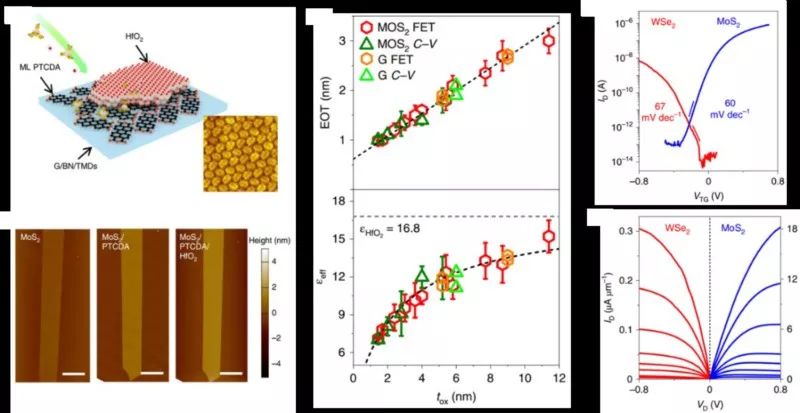

二维半导体材料具有非零带隙、极限沟道厚度、高迁移率等特点,可以显著增加栅极调控能力,是有希望继续延伸摩尔定律的新型电子材料。然而,由于二维材料表面无悬挂键,无法利用传统原子层沉积工艺沉积高质量栅极介质层,导致界面态和等效氧化层厚度(EOT)远高于硅基CMOS晶体管。因此,开发针对二维材料的高质量、超薄、并且与大面积工艺兼容的介质层集成工艺,是二维电子器件应用的关键瓶颈之一。

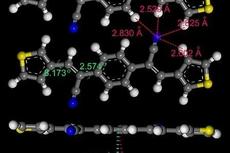

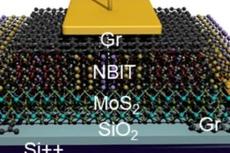

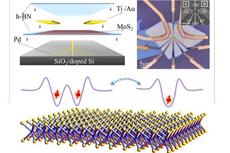

为了解决上述难题,南京大学王欣然、施毅教授团队开展国际合作,利用了二维材料与分子之间的范德瓦尔斯作用,以0.3纳米厚的单层分子晶体作为界面层,在二维材料上成功实现了高质量、超薄high-κ介质层沉积技术。凭借该技术,团队首次在石墨烯、MoS2和WSe2等二维材料上实现了1 nm EOT,并具备原子级的平整度、低界面态密度和高击穿电场。重要的是,介质层的漏电流密度与CMOS水平相当,满足了国际半导体技术路线图对低功耗逻辑晶体管的要求。

超薄high-k介质层在二维材料上的沉积及其低功耗晶体管

利用分子辅助的超薄介质层沉积技术,研究人员将二维半导体场效应晶体管的亚阈值摆幅降至60 mV/dec的理论极限,工作电压降至0.8 V,并且在20 nm沟道长度下未发现显著的短沟道效应。进一步,实现了功耗小于1 nW的二维CMOS逻辑反相器,并通过石墨烯射频器件验证了介质层可以工作在10 GHz以上。值得指出的是,该技术适用于多种二维材料,并兼容大面积化学气相沉积样品。

此项研究突破了二维电子器件超薄介电层集成这一瓶颈,有望推动二维集成电路的发展,该工作以《Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices》为题近期发表于Nature Electronics。参与合作的单位包括加州大学洛杉矶分校Xiangfeng Duan教授、新加坡国立大学Wei Chen教授、东京大学K. Nagashio教授、南京大学王鹏和马海波教授、中电55所陈堂胜研究员等课题组。该研究得到了基金委重点项目、创新群体项目、应急管理项目、科技部量子调控青年科学家专题以及中科院战略性先导科技专项等项目的资助。来源 南京大学新闻网

论文链接:

https://www.nature.com/articles/s41928-019-0334-y

来源:mse_material 材料科学与工程

原文链接:https://mp.weixin.qq.com/s?__biz=MzA4NDk3ODEwNQ==&mid=2698823354&idx=3&sn=cb5075b12f73763bc7620b5966439ed7&chksm=baf6966c8d811f7a6217a84e162cfecbafe3bd0973654a0f7e164b08a8adbdf1a627dac6e439#rd

版权声明:除非特别注明,本站所载内容来源于互联网、微信公众号等公开渠道,不代表本站观点,仅供参考、交流、公益传播之目的。转载的稿件版权归原作者或机构所有,如有侵权,请联系删除。

电话:(010)86409582

邮箱:kejie@scimall.org.cn

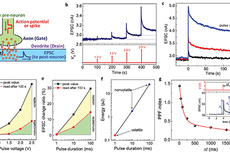

基于二维层状氧化钼的全固态神经突触晶体管

工业硅片上长出“完美”二维超薄材料,可用于制造下一代晶体管和电子薄膜

二维有机单晶p-n结用于双极晶体管

物理所制备基于二维层状氧化钼的全固态神经突触晶体管

二维有机单晶的缺陷研究及高性能场效应发光晶体管

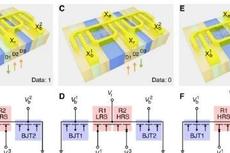

研究透视:Science-二维铁电材料-同构晶体管存储器架构,用于神经形态硬件集成系统

研究进展:Advanced Materials - 二维铁电场效应晶体管获重要进展

二维材料半导体量子晶体管研究取得新进展 实现有效电学调控

重新定义数据处理的能源效率,具有千个晶体管的二维半导体问世

二维异质结的新机遇:制作超陡亚阈值摆幅晶体管