孙熙宸

加好友

孙熙宸 2019-12-09

来源:中科院微电子研究所

垂直纳米环栅晶体管是集成电路2纳米及以下技术代的主要候选器件,但其在提高器件性能和可制造性等方面面临着众多挑战。在2018年底举办的国际集成电路会议IEDM上,来自IMEC的Ryckaert博士1将垂直纳米器件的栅极长度及沟道与栅极相对位置的控制列为关键挑战之一。

微电子所先导中心朱慧珑研究员及其课题组从2016年起针对相关基础器件和关键工艺开展了系统研究,提出并实现了世界上首个具有自对准栅极的叠层垂直纳米环栅晶体管(Vertical Sandwich Gate-All-Around FETs或VSAFETs),获得多项中、美发明专利授权,研究成果近日发表在国际微电子器件领域的顶级期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2954537)。

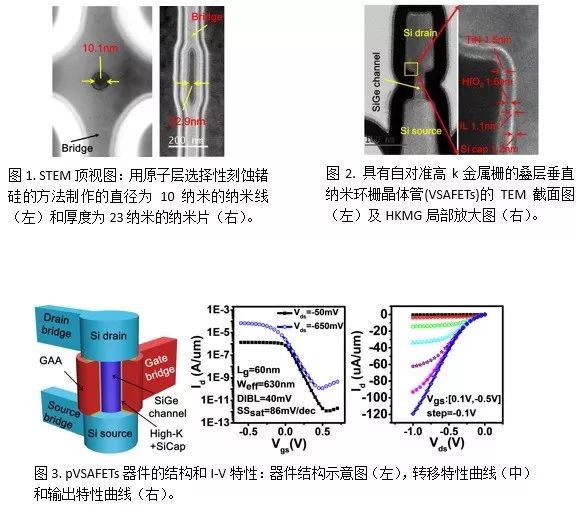

朱慧珑课题组系统地研发了一种原子层选择性刻蚀锗硅的方法,结合多层外延生长技术将此方法用于锗硅/硅超晶格叠层的选择性刻蚀,从而精确地控制纳米晶体管沟道尺寸和有效栅长;首次研发出了垂直纳米环栅晶体管的自对准高k金属栅后栅工艺;其集成工艺与主流先进CMOS制程兼容。课题组最终制造出了栅长60纳米,纳米片厚度20纳米的p型VSAFET。原型器件的SS、DIBL和电流开关比(Ion/Ioff)分别为86mV/dec、40mV和1.8E+5。

该项目部分得到中国科学院集成电路创新研究院项目(Y7YC01X001)的资助。

References:

J.Ryckaert, "3D integration fordensity and functionality," in 2018 IEEE International ElectronDevices Meeting (IEDM), short course, San Francisco, USA, 2018.

来源:imecas_wx 中科院微电子研究所

原文链接:http://mp.weixin.qq.com/s?__biz=MjM5Mjk2MzU1Ng==&mid=2651730241&idx=1&sn=ac93225046eb4d8577a392f7dad3417e&chksm=bd64dfca8a1356dc25ffe3c1fb39dd890e6f76abac891f60de22fd88a6ae7a438076038bc867&scene=27#wechat_redirect

版权声明:除非特别注明,本站所载内容来源于互联网、微信公众号等公开渠道,不代表本站观点,仅供参考、交流、公益传播之目的。转载的稿件版权归原作者或机构所有,如有侵权,请联系删除。

电话:(010)86409582

邮箱:kejie@scimall.org.cn

集成电路设计

集成电路企业20强榜单出炉,看纳米城里的“芯”力量!

第二期“千人讲堂”开讲

中国微米纳米技术学会第十八届学术年会暨微系统与纳米工程高层论坛

【走近桂籍科学家】用纳米武装电池新世界

中国集成电路发展要回归应用 ——院士圆桌会议热议中国集成电路发展

新集成电路技术或可使太赫兹微芯片成为现实

集成电路产业基金投资布局

集成电路装备

30万人才缺口拦路集成电路发展